# **User Manual**

# **BMP561**

Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ Core-based 32-bit MCU

Version: V1.0

© Geehy Semiconductor Co., Ltd.

# Contents

| 1                                                              | Introduction and Document Description Rules                                                                                                                                                                                                                                                                                    | 5                                                              |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1.1                                                            | Introduction                                                                                                                                                                                                                                                                                                                   | 5                                                              |

| 2                                                              | System Architecture                                                                                                                                                                                                                                                                                                            | 6                                                              |

| 2.1                                                            | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                | 6                                                              |

| 2.2                                                            | System architecture block diagram                                                                                                                                                                                                                                                                                              | 6                                                              |

| 3                                                              | System Control (SYSCTRL)                                                                                                                                                                                                                                                                                                       | 7                                                              |

| 3.1                                                            | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                | 7                                                              |

| 3.2                                                            | Introduction                                                                                                                                                                                                                                                                                                                   | 7                                                              |

| 3.3                                                            | Register address mapping                                                                                                                                                                                                                                                                                                       | 7                                                              |

| 3.4                                                            | Register functional description                                                                                                                                                                                                                                                                                                | 8                                                              |

| 4                                                              | Flash Memory (FLASH)                                                                                                                                                                                                                                                                                                           | 21                                                             |

| 4.1                                                            | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                | 21                                                             |

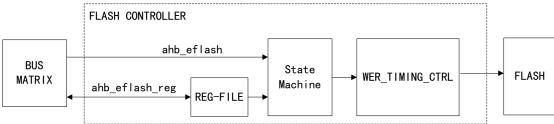

| 4.2                                                            | Introduction                                                                                                                                                                                                                                                                                                                   | 21                                                             |

| 4.3                                                            | Main characteristics                                                                                                                                                                                                                                                                                                           | 21                                                             |

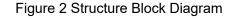

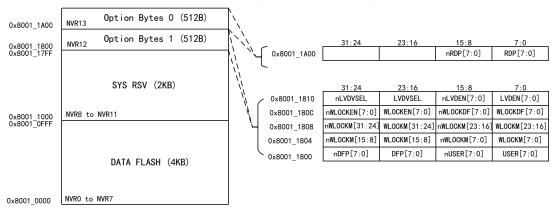

| 4.4                                                            | Structure block diagram                                                                                                                                                                                                                                                                                                        | 21                                                             |

| 4.5                                                            | Functional description                                                                                                                                                                                                                                                                                                         | 22                                                             |

| 4.6                                                            | Register address mapping                                                                                                                                                                                                                                                                                                       | 29                                                             |

| 4.7                                                            | Register functional description                                                                                                                                                                                                                                                                                                | 29                                                             |

| 5                                                              | Clock Management Unit (CMU)                                                                                                                                                                                                                                                                                                    | 34                                                             |

| 5.1                                                            | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                | 34                                                             |

| 5.2                                                            | Introduction                                                                                                                                                                                                                                                                                                                   | 34                                                             |

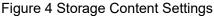

| 5.3                                                            | Clock source                                                                                                                                                                                                                                                                                                                   | 34                                                             |

| 5.4                                                            |                                                                                                                                                                                                                                                                                                                                |                                                                |

|                                                                | Clock tree                                                                                                                                                                                                                                                                                                                     | 35                                                             |

| 5.5                                                            | Clock tree<br>Clock enable and master clock switching                                                                                                                                                                                                                                                                          |                                                                |

| 5.5<br>5.6                                                     |                                                                                                                                                                                                                                                                                                                                | 35                                                             |

|                                                                | Clock enable and master clock switching                                                                                                                                                                                                                                                                                        | 35<br>36                                                       |

| 5.6                                                            | Clock enable and master clock switching<br>Register address mapping                                                                                                                                                                                                                                                            | 35<br>36<br>36                                                 |

| 5.6<br>5.7                                                     | Clock enable and master clock switching<br>Register address mapping<br>Register functional description                                                                                                                                                                                                                         | 35<br>36<br>36<br><b>37</b>                                    |

| 5.6<br>5.7<br><b>6</b>                                         | Clock enable and master clock switching<br>Register address mapping<br>Register functional description<br>Nested Vector Interrupt Controller (NVIC)                                                                                                                                                                            | 35<br>36<br>36<br><b>37</b><br>37                              |

| 5.6<br>5.7<br><b>6</b><br>6.1                                  | Clock enable and master clock switching<br>Register address mapping<br>Register functional description<br><b>Nested Vector Interrupt Controller (NVIC)</b><br>Full Name and Abbreviation Description of Terms                                                                                                                  | 35<br>36<br>36<br><b>37</b><br>37<br>37                        |

| 5.6<br>5.7<br><b>6</b><br>6.1<br>6.2                           | Clock enable and master clock switching<br>Register address mapping<br>Register functional description<br><b>Nested Vector Interrupt Controller (NVIC)</b><br>Full Name and Abbreviation Description of Terms<br>Introduction                                                                                                  | 35<br>36<br>36<br><b>37</b><br>37<br>37<br>37                  |

| 5.6<br>5.7<br><b>6</b><br>6.1<br>6.2<br>6.3                    | Clock enable and master clock switching<br>Register address mapping<br>Register functional description<br><b>Nested Vector Interrupt Controller (NVIC)</b><br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics                                                                          | 35<br>36<br>36<br><b>37</b><br>37<br>37<br>37<br>37            |

| 5.6<br>5.7<br><b>6</b><br>6.1<br>6.2<br>6.3<br>6.4             | Clock enable and master clock switching<br>Register address mapping<br>Register functional description<br><b>Nested Vector Interrupt Controller (NVIC)</b><br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics<br>Interrupt vector table                                                | 35<br>36<br>37<br>37<br>37<br>37<br>37<br>37<br><b>39</b>      |

| 5.6<br>5.7<br><b>6</b><br>6.1<br>6.2<br>6.3<br>6.4<br><b>7</b> | Clock enable and master clock switching<br>Register address mapping<br>Register functional description<br><b>Nested Vector Interrupt Controller (NVIC)</b><br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics<br>Interrupt vector table<br><b>External Interrupt Controller (EINT)</b> | 35<br>36<br>36<br>37<br>37<br>37<br>37<br>37<br>37<br>39<br>39 |

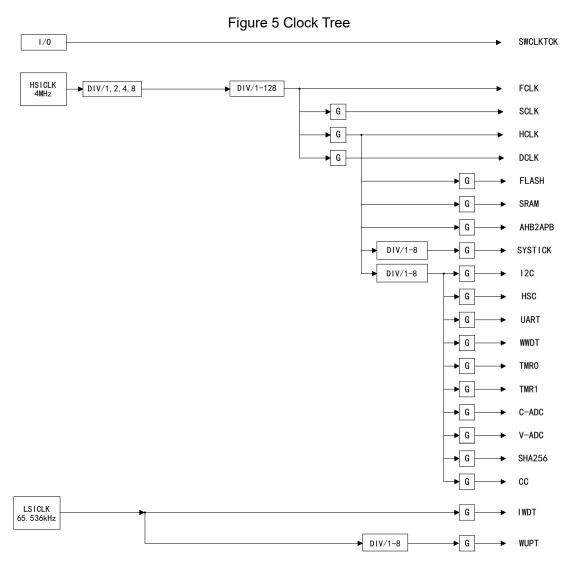

| 7.4                                                                                                                                                                                            | Structure block diagram                                                                                                                                                                                                                                                                                                                                                                                                        | . 39                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 7.5                                                                                                                                                                                            | Functional description                                                                                                                                                                                                                                                                                                                                                                                                         | . 39                                                                                    |

| 7.6                                                                                                                                                                                            | Register address mapping                                                                                                                                                                                                                                                                                                                                                                                                       | .40                                                                                     |

| 7.7                                                                                                                                                                                            | Register functional description                                                                                                                                                                                                                                                                                                                                                                                                | .40                                                                                     |

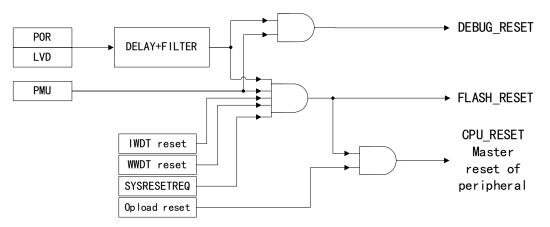

| 8                                                                                                                                                                                              | Reset Management Unit (RMU)                                                                                                                                                                                                                                                                                                                                                                                                    | .43                                                                                     |

| 8.1                                                                                                                                                                                            | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                                                                                                                | .43                                                                                     |

| 8.2                                                                                                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                   | .43                                                                                     |

| 8.3                                                                                                                                                                                            | Main characteristics                                                                                                                                                                                                                                                                                                                                                                                                           | .43                                                                                     |

| 8.4                                                                                                                                                                                            | Structure block diagram                                                                                                                                                                                                                                                                                                                                                                                                        | .43                                                                                     |

| 8.5                                                                                                                                                                                            | Functional description                                                                                                                                                                                                                                                                                                                                                                                                         | .44                                                                                     |

| 8.6                                                                                                                                                                                            | Register address mapping                                                                                                                                                                                                                                                                                                                                                                                                       | .45                                                                                     |

| 8.7                                                                                                                                                                                            | Register functional description                                                                                                                                                                                                                                                                                                                                                                                                | .45                                                                                     |

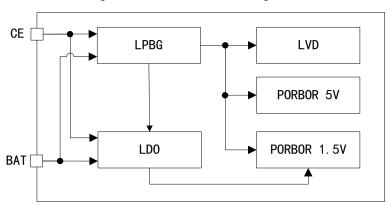

| 9                                                                                                                                                                                              | Power Management Unit (PMU)                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                                                                      |

| 9.1                                                                                                                                                                                            | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                                                                                                                | .46                                                                                     |

| 9.2                                                                                                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                   | .46                                                                                     |

| 9.3                                                                                                                                                                                            | Main characteristics                                                                                                                                                                                                                                                                                                                                                                                                           | .46                                                                                     |

| 9.4                                                                                                                                                                                            | Structure block diagram                                                                                                                                                                                                                                                                                                                                                                                                        | .47                                                                                     |

| 9.5                                                                                                                                                                                            | Functional description                                                                                                                                                                                                                                                                                                                                                                                                         | .47                                                                                     |

| 9.6                                                                                                                                                                                            | Register address mapping                                                                                                                                                                                                                                                                                                                                                                                                       | .51                                                                                     |

| 07                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

| 9.7                                                                                                                                                                                            | Register functional description                                                                                                                                                                                                                                                                                                                                                                                                | .51                                                                                     |

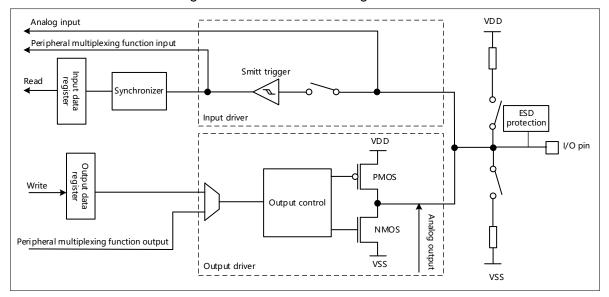

| 9.7<br><b>10</b>                                                                                                                                                                               | Register functional description         General-Purpose Input/Output Pin (GPIO)                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

|                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                | .52                                                                                     |

| 10                                                                                                                                                                                             | General-Purpose Input/Output Pin (GPIO)                                                                                                                                                                                                                                                                                                                                                                                        | . <b>52</b><br>. 52                                                                     |

| <b>10</b><br>10.1                                                                                                                                                                              | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                                                                     | . <b>52</b><br>. 52<br>. 52                                                             |

| <b>10</b><br>10.1<br>10.2                                                                                                                                                                      | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms<br>Introduction                                                                                                                                                                                                                                                                                                                     | . <b>52</b><br>. 52<br>. 52<br>. 52                                                     |

| <b>10</b><br>10.1<br>10.2<br>10.3                                                                                                                                                              | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics                                                                                                                                                                                                                                                                                             | . <b>52</b><br>. 52<br>. 52<br>. 52<br>. 53                                             |

| <b>10</b><br>10.1<br>10.2<br>10.3<br>10.4                                                                                                                                                      | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics<br>Structure block diagram                                                                                                                                                                                                                                                                  | . <b>52</b><br>. 52<br>. 52<br>. 52<br>. 53<br>. 53                                     |

| <b>10</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5                                                                                                                                              | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics .<br>Structure block diagram.<br>Functional description                                                                                                                                                                                                                                   | . <b>52</b><br>. 52<br>. 52<br>. 52<br>. 53<br>. 53<br>. 54                             |

| <b>10</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6                                                                                                                                      | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics<br>Structure block diagram<br>Functional description<br>Register address mapping                                                                                                                                                                                                          | .52<br>.52<br>.52<br>.53<br>.53<br>.54<br>.54                                           |

| <b>10</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7                                                                                                                              | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics<br>Structure block diagram<br>Functional description<br>Register address mapping<br>Register functional description                                                                                                                                                                         | .52<br>.52<br>.52<br>.53<br>.53<br>.54<br>.54<br>.54                                    |

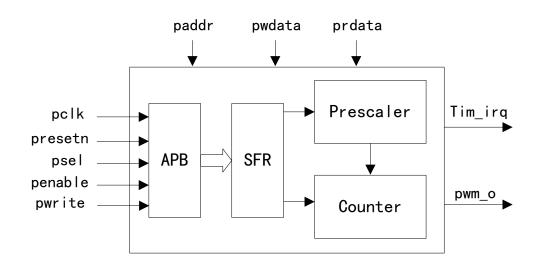

| <ol> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>10.6</li> <li>10.7</li> <li>11</li> </ol>                                                                       | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics<br>Structure block diagram<br>Functional description<br>Register address mapping<br>Register functional description.<br>Timer (TMR0/1).                                                                                                                                                   | .52<br>.52<br>.52<br>.53<br>.53<br>.53<br>.54<br>.54<br>.54<br>.62                      |

| <b>10</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br><b>11</b><br>11.1                                                                                                         | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics<br>Structure block diagram.<br>Functional description<br>Register address mapping.<br>Register functional description.<br>Timer (TMR0/1).<br>Full Name and Abbreviation Description of Terms.                                                                                             | .52<br>.52<br>.52<br>.53<br>.53<br>.54<br>.54<br>.62<br>.62                             |

| <b>10</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br><b>11</b><br>11.1<br>11.2                                                                                                 | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics<br>Structure block diagram.<br>Functional description<br>Register address mapping.<br>Register functional description.<br><b>Timer (TMR0/1)</b> .<br>Full Name and Abbreviation Description of Terms.<br>Introduction.                                                                    | .52<br>.52<br>.52<br>.53<br>.53<br>.53<br>.54<br>.54<br>.54<br>.62<br>.62               |

| <ol> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>10.6</li> <li>10.7</li> <li>11.1</li> <li>11.2</li> <li>11.3</li> </ol>                                         | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics .<br>Structure block diagram .<br>Functional description .<br>Register address mapping .<br>Register functional description .<br>Timer (TMR0/1).<br>Full Name and Abbreviation Description of Terms.<br>Introduction<br>Main characteristics .                                            | .52<br>.52<br>.52<br>.53<br>.53<br>.54<br>.54<br>.62<br>.62<br>.62<br>.62               |

| <ul> <li>10</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>10.6</li> <li>10.7</li> <li>11.1</li> <li>11.2</li> <li>11.3</li> <li>11.4</li> </ul>               | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics<br>Structure block diagram<br>Functional description<br>Register address mapping<br>Register functional description<br>Timer (TMR0/1)<br>Full Name and Abbreviation Description of Terms<br>Introduction<br>Main characteristics<br>Structure block diagram                                 | .52<br>.52<br>.52<br>.53<br>.53<br>.54<br>.62<br>.62<br>.62<br>.62<br>.63<br>.63        |

| <ul> <li>10</li> <li>10.1</li> <li>10.2</li> <li>10.3</li> <li>10.4</li> <li>10.5</li> <li>10.6</li> <li>10.7</li> <li>11.1</li> <li>11.2</li> <li>11.3</li> <li>11.4</li> <li>11.5</li> </ul> | General-Purpose Input/Output Pin (GPIO)<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics<br>Structure block diagram<br>Functional description<br>Register address mapping<br>Register functional description.<br>Timer (TMR0/1).<br>Full Name and Abbreviation Description of Terms.<br>Introduction.<br>Main characteristics<br>Structure block diagram<br>Functional description | .52<br>.52<br>.52<br>.53<br>.53<br>.54<br>.62<br>.62<br>.62<br>.62<br>.63<br>.63<br>.64 |

| 12.1 | Full Name and Abbreviation Description of Terms    | 67  |

|------|----------------------------------------------------|-----|

| 12.2 | Introduction                                       | 67  |

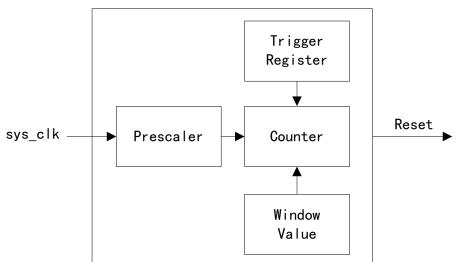

| 12.3 | Independent watchdog timer (IWDT)                  | 67  |

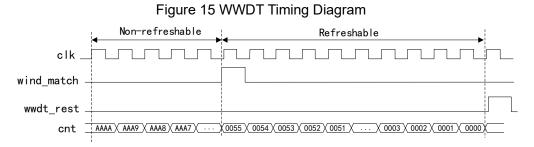

| 12.4 | Window watchdog (WWDT)                             | 71  |

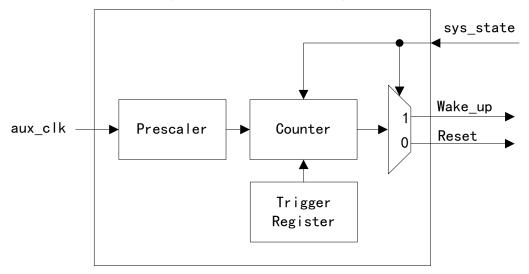

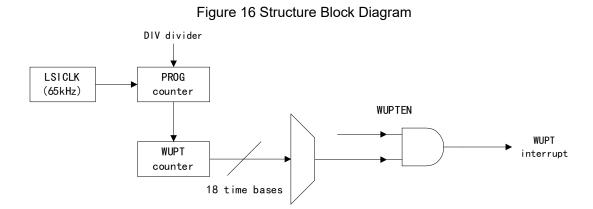

| 13   | Wake-Up Timer (WUPT)                               | 76  |

| 13.1 | Full Name and Abbreviation Description of Terms    | 76  |

| 13.2 | Introduction                                       | 76  |

| 13.3 | Main characteristics                               | 76  |

| 13.4 | Structure block diagram                            | 76  |

| 13.5 | Functional description                             | 76  |

| 13.6 | Register address mapping                           | 77  |

| 13.7 | Register functional description                    | 77  |

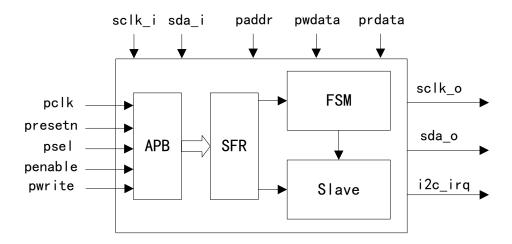

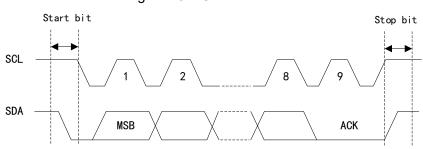

| 14   | Internal Integrated Circuit Interface (I2C)        | 79  |

| 14.1 | Full Name and Abbreviation Description of Terms    | 79  |

| 14.2 | Introduction                                       | 79  |

| 14.3 | Main characteristics                               | 79  |

| 14.4 | Structure block diagram                            | 80  |

| 14.5 | Functional description                             | 80  |

| 14.6 | Register address mapping                           | 86  |

| 14.7 | Register functional description                    | 87  |

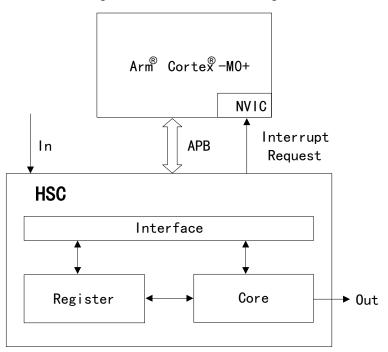

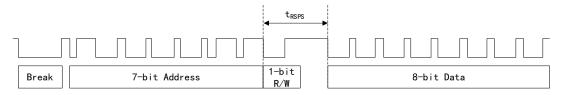

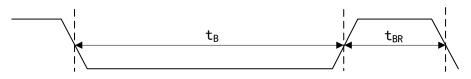

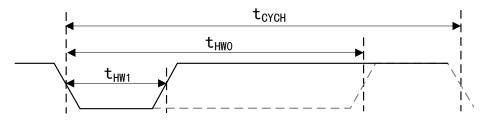

| 15   | Single-Wire Communication Interface (HSC)          | 93  |

| 15.1 | Full Name and Abbreviation Description of Terms    | 93  |

| 15.2 | Introduction                                       | 93  |

| 15.3 | Main characteristics                               | 93  |

| 15.4 | Structure block diagram                            | 94  |

| 15.5 | Functional description                             | 94  |

| 15.6 | Register address mapping                           | 95  |

| 15.7 | Register functional description                    | 96  |

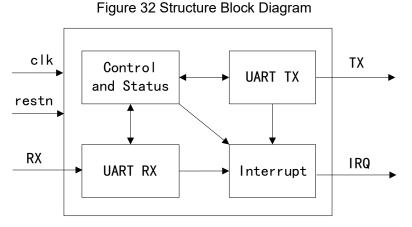

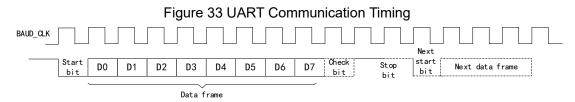

| 16   | Universal Asynchronous Receiver/Transmitter (UART) | 100 |

| 16.1 | Full Name and Abbreviation Description of Terms    | 100 |

| 16.2 | Introduction                                       | 100 |

| 16.3 | Main characteristics                               | 100 |

| 16.4 | Structure block diagram                            | 101 |

| 16.5 | Functional description                             | 101 |

| 16.6 | Register address mapping                           | 101 |

| 40 7 |                                                    |     |

| 16.7 | Register functional description                    | 102 |

| 19   | Revision history                                | 122 |

|------|-------------------------------------------------|-----|

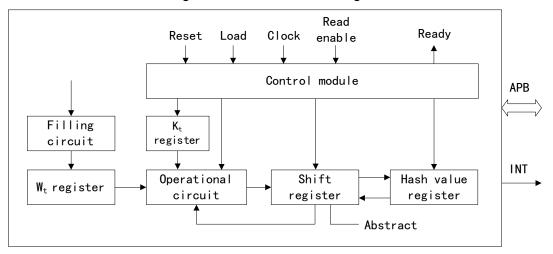

| 18.7 | Register functional description                 | 115 |

| 18.6 | Register address mapping                        | 114 |

| 18.5 | Functional description                          | 114 |

| 18.4 | Structure block diagram                         | 113 |

| 18.3 | Main characteristics                            | 113 |

| 18.2 | Introduction                                    | 113 |

| 18.1 | Full Name and Abbreviation Description of Terms | 113 |

| 18   | Hash Algorithm (SHA256)                         | 113 |

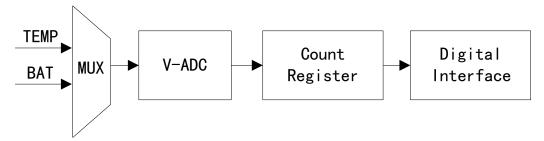

| 17.3 | V-ADC converter                                 | 110 |

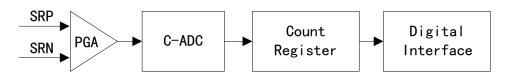

| 17.2 | C-ADC converter                                 | 107 |

| 17.1 | Full Name and Abbreviation Description of Terms | 107 |

## **1** Introduction and Document Description Rules

## 1.1 Introduction

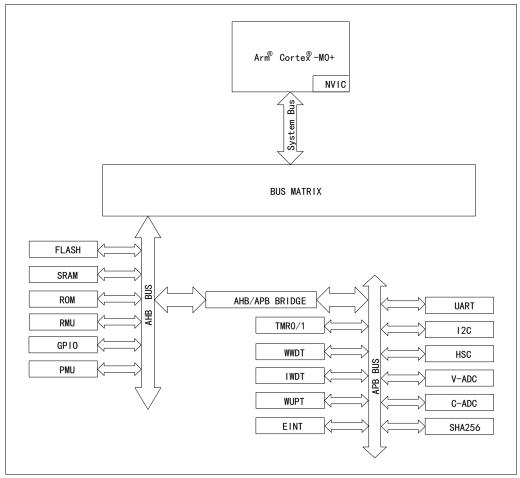

BMP561 is a gauge chip, with the core based on Arm<sup>®</sup> Cortex<sup>®</sup>-M0+, and the system bus is based on the AHB-Lite advanced high-performance bus protocol. It can achieve fast processing and storage of data in combination with high-speed memory. The peripheral bus is based on the APB advanced peripheral bus protocol and can be used to expand rich peripherals, ensuring fast and flexible connection.

For information about Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ core, refer to *Technical Reference Manual of Arm<sup>®</sup> Cortex<sup>®</sup>-M0*+. For model information, dimensions and electrical characteristics of components, refer to the corresponding datasheet.

We hereby declare that: Zhuhai Geehy Semiconductor Co., Ltd. is hereinafter referred to as "Geehy".

# 2 System Architecture

## 2.1 Full Name and Abbreviation Description of Terms

| Full name in English          | English abbreviation |

|-------------------------------|----------------------|

| Advanced High-Performance Bus | AHB                  |

| Advanced Peripheral Bus       | APB                  |

Table 1 Full Name and Abbreviation Description of Terms

## 2.2 System architecture block diagram

Figure 1 System Architecture Block Diagram

# 3 System Control (SYSCTRL)

## 3.1 Full Name and Abbreviation Description of Terms

Table 2 Full Name and Abbreviation Description of Terms

| Full name in English | English abbreviation |

|----------------------|----------------------|

| System Control       | SYSCTRL              |

## 3.2 Introduction

The system control module includes power management, clock management, reset management, and other system related control. For detailed information, refer to the corresponding chapter of each module.

## 3.3 Register address mapping

| Register name    | Description                                                  | Offset address |  |

|------------------|--------------------------------------------------------------|----------------|--|

| SYSCTRL_KEY      | Unlock register                                              | 0x00           |  |

| SYSCTRL_SCCR     | Master clock control register                                | 0x04           |  |

| SYSCTRL_AHBBCG   | AHB clock gating register                                    | 0x08           |  |

| SYSCTRL_APBBCG   | APB peripheral bus clock gating register                     | 0x0C           |  |

| SYSCTRL_APBWCG   | APB peripheral work clock gating register                    | 0x10           |  |

| SYSCTRL_AHBRSTCR | AHB peripheral reset control register                        | 0x14           |  |

| SYSCTRL_APBRSTCR | APB peripheral reset control register                        | 0x18           |  |

| SYSCTRL_RSTSR    | System reset source state register                           | 0x1C           |  |

| SYSCTRL_LPMCR    | System low-power mode register                               | 0x20           |  |

| SYSCTRL_LPCR     | System low-power configuration register                      | 0x24           |  |

| SYSCTRL_STA      | System communication start bit detection register            | 0x28           |  |

| SYSCTRL_WUSR     | System wake-up flag register                                 | 0x2C           |  |

| SYSCTRL_RSTSRCLR | System reset source state clear register                     | 0x30           |  |

| SYSCTRL_STACLR   | System communication start bit detection flag clear register | 0x34           |  |

| SYSCTRL_WUSRCLR  | System wake-up flag clear register                           | 0x38           |  |

| SYSCTRL_HSICLKCR | HSI clock control register                                   | 0x3C           |  |

| SYSCTRL_LSICLKCR | LSI clock control register                                   | 0x40           |  |

| SYSCTRL_ANACR    | System analog peripheral control register 0x                 |                |  |

Table 3 SYSCTRL Register Address Mapping

| Register name   | Description                   | Offset address |

|-----------------|-------------------------------|----------------|

| SYSCTRL_DEBUGCR | System debug control register | 0x48           |

| SYSCTRL_BOOTCR  | System BOOT control register  | 0x4C           |

## 3.4 Register functional description

#### 3.4.1 Unlock register (SYSCTRL\_KEY)

Offset address: 0x00

Reset value: 0x0000 0000

| Field | Name    | R/W      | Description                                                                                                                                                                                                                                                                                        |

|-------|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0  | LOCKKEY | W        | <ul> <li>Lock Key</li> <li>Password protection configuration for system register write operation:</li> <li>1. Before operating on the SYSCTRL system register, it must be unlocked by writing 0x87E4 to the Key value.</li> <li>2. After unlocking the system register, the KEYST0 flag</li> </ul> |

| 16    | KEYST   | W        | bit will be set, and writing 1 to this bit will lock it.<br>Key Status<br>After unlocking the system register, the KEYST flag bit will<br>be set, and writing 1 to this bit will lock it.<br>Note: Writing 0 is invalid, and writing 1 will lock it.                                               |

| 31:17 |         | Reserved |                                                                                                                                                                                                                                                                                                    |

#### 3.4.2 Master clock control register (SYSCTRL\_SCCR)

Offset address: 0x04

| Field      | Name      | R/W           | Description                                             |

|------------|-----------|---------------|---------------------------------------------------------|

|            |           |               | SYSCLK Division                                         |

|            |           |               | 0: 1 frequency division (no frequency division)         |

| 2:0        | SYSCLKDIV | R/W           | 1: 2 frequency division                                 |

|            |           |               |                                                         |

|            |           |               | N: 2 <sup>N</sup> frequency division                    |

|            |           |               | SYSCLK Select                                           |

| 3          | SYSCLKSEL | R/W           | 0: Select HSICLK                                        |

|            |           |               | 1: Select LSICLK                                        |

|            |           |               | HSICLK Division                                         |

|            | APBCLKDIV | APBCLKDIV R/W | 0: 1 frequency division (no frequency division)         |

| <b>5</b> 4 |           |               | 1: 2 frequency division                                 |

| 5:4        |           |               | 2: 4 frequency division                                 |

|            |           |               | 3: 8 frequency division                                 |

|            |           |               | Note: The default value is to be determined             |

|            |           |               | Switch Busy                                             |

| 6          | SWBUSY    | R             | 0: In progress of clock switching or no clock switching |

|            |           |               | 1: In progress of clock switching                       |

| 31:7       | Reserved  |               |                                                         |

# 3.4.3 AHB clock gating register (SYSCTRL\_AHBBCG)

Offset address: 0x08

Reset value: 0x0000 000F

| Field | Name       | R/W | Description             |

|-------|------------|-----|-------------------------|

|       |            |     | FLASH Bus Clock Enable  |

| 0     | FLSBCEN    | R/W | 0: Disable              |

|       |            |     | 1: Enable               |

|       |            |     | GPIO Bus Clock Enable   |

| 1     | GPIOBCEN   | R/W | 0: Disable              |

|       |            |     | 1: Enable               |

|       |            |     | AHB to APB Clock Enable |

| 2     | AHB2APBCEN | R/W | 0: Disable              |

|       |            |     | 1: Enable               |

|       |            |     | ROM Bus Clock Enable    |

| 3     | ROMBCEN    | R/W | 0: Disable              |

|       |            |     | 1: Enable               |

| 31:4  |            |     | Reserved                |

## 3.4.4 APB peripheral bus clock gating register (SYSCTRL\_APBBCG) Offset address: 0x0C

| Field | Name     | R/W | Description            |

|-------|----------|-----|------------------------|

|       |          |     | WWDT Bus Clock Enable  |

| 0     | WWDTBCEN | R/W | 0: Disable             |

|       |          |     | 1: Enable              |

|       |          |     | I2C Bus Clock Enable   |

| 1     | I2CBCEN  | R/W | 0: Disable             |

|       |          |     | 1: Enable              |

|       |          |     | HSC Bus Clock Enable   |

| 2     | HSCBCEN  | R/W | 0: Disable             |

|       |          |     | 1: Enable              |

|       |          |     | TMR0 Bus Clock Enable  |

| 3     | TMR0BCEN | R/W | 0: Disable             |

|       |          |     | 1: Enable              |

|       |          |     | TMR1 Bus Clock Enable  |

| 4     | TMR1BCEN | R/W | 0: Disable             |

|       |          |     | 1: Enable              |

|       |          |     | C-ADC Bus Clock Enable |

| 5     | ADC0BCEN | R/W | 0: Disable             |

|       |          |     | 1: Enable              |

|       |          |     | V-ADC Bus Clock Enable |

| 6     | ADC1BCEN | R/W | 0: Disable             |

|       |          |     | 1: Enable              |

| 7     |          |     | Reserved               |

| 8     | UARTBCEN | R/W | UART Bus Clock Enable  |

| Field | Name     | R/W | Description           |  |

|-------|----------|-----|-----------------------|--|

|       |          |     | 0: Disable            |  |

|       |          |     | 1: Enable             |  |

|       |          |     | SHA Bus Clock Enable  |  |

| 9     | SHABCEN  | R/W | 0: Disable            |  |

|       |          |     | 1: Enable             |  |

|       |          |     | IWDT Bus Clock Enable |  |

| 10    | IWDTBCEN | R/W | 0: Disable            |  |

|       |          |     | 1: Enable             |  |

|       |          |     | WUPT Bus Clock Enable |  |

| 11    | WUPTBCEN | R/W | 0: Disable            |  |

|       |          |     | 1: Enable             |  |

|       |          |     | EINT Bus Clock Enable |  |

| 12    | EINTBCEN | R/W | 0: Disable            |  |

|       |          |     | 1: Enable             |  |

| 31:13 | Reserved |     |                       |  |

Note: When accessing the module register, it is necessary to ensure that the corresponding work clock of the module has been enabled; otherwise, some registers of some modules not to be able to be written to.

## 3.4.5 APB peripheral work clock gating register (SYSCTRL\_APBWCG) Offset address: 0x10

| Field | Name     | R/W     | Description             |

|-------|----------|---------|-------------------------|

|       |          |         | WWDT Work Clock Enable  |

| 0     | WWDTWCEN | R/W     | 0: Disable              |

|       |          |         | 1: Enable               |

|       |          |         | I2C2 Work Clock Enable  |

| 1     | I2CWCEN  | R/W     | 0: Disable              |

|       |          |         | 1: Enable               |

|       |          |         | HSC Work Clock Enable   |

| 2     | HSCWCEN  | R/W     | 0: Disable              |

|       |          |         | 1: Enable               |

|       |          |         | TMR0 Work Clock Enable  |

| 3     | TMR0WCEN | R/W     | 0: Disable              |

|       |          |         | 1: Enable               |

|       |          |         | TMR1 Work Clock Enable  |

| 4     | TMR1WCEN | R/W     | 0: Disable              |

|       |          |         | 1: Enable               |

|       |          |         | C-ADC Work Clock Enable |

| 5     | ADC0WCEN | R/W     | 0: Disable              |

|       |          |         | 1: Enable               |

|       |          |         |                         |

| 6     | ADC1WCEN | R/W     | V-ADC Work Clock Enable |

| 0     | ADCINCEN | Γ\/ V V | 0: Disable              |

|       |          |         | 1: Enable               |

| Field | Name     | R/W      | Description                                       |  |  |

|-------|----------|----------|---------------------------------------------------|--|--|

| 7     |          | Reserved |                                                   |  |  |

| 8     | UARTWCEN | R/W      | UART Work Clock Enable<br>0: Disable<br>1: Enable |  |  |

| 9     | SHAWCEN  | R/W      | SHA Work Clock Enable<br>0: Disable<br>1: Enable  |  |  |

| 10    | IWDTWCEN | R/W      | IWDT Work Clock Enable<br>0: Disable<br>1: Enable |  |  |

| 11    | WUPTWCEN | R/W      | WUPT Work Clock Enable<br>0: Disable<br>1: Enable |  |  |

| 12    | EINTWCEN | R/W      | EINT Work Clock Enable<br>0: Disable<br>1: Enable |  |  |

| 31:13 | Reserved |          |                                                   |  |  |

## **3.4.6 AHB peripheral reset control register (SYSCTRL\_AHBRSTCR)** Offset address: 0x14

Reset value: 0x0000 0003

| Field | Name     | R/W | Description |

|-------|----------|-----|-------------|

|       |          |     | FLASH Reset |

| 0     | FLSRST   | R/W | 0: Reset    |

|       |          |     | 1: Release  |

|       |          |     | GPIO Reset  |

| 1     | GPIORST  | R/W | 0: Reset    |

|       |          |     | 1: Release  |

| 31:2  | Reserved |     |             |

## **3.4.7** APB peripheral reset control register (SYSCTRL\_APBRSTCR) Offset address: 0x18

Reset value: 0x0000 1FFF

| Field | Name    | R/W | Description |

|-------|---------|-----|-------------|

|       |         |     | WWDT Reset  |

| 0     | WWDTRST | R/W | 0: Reset    |

|       |         |     | 1: Release  |

|       |         |     | I2C Reset   |

| 1     | I2CRST  | R/W | 0: Reset    |

|       |         |     | 1: Release  |

|       |         |     | HSC Reset   |

| 2     | HSCRST  | R/W | 0: Reset    |

|       |         |     | 1: Release  |

| Field | Name     | R/W | Description |  |  |  |

|-------|----------|-----|-------------|--|--|--|

|       |          |     | TMR0 Reset  |  |  |  |

| 3     | TMR0RST  | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

|       |          |     | TMR1 Reset  |  |  |  |

| 4     | TMR1RST  | R/W | 0: Disable  |  |  |  |

|       |          |     | 1: Enable   |  |  |  |

|       |          |     | C-ADC Reset |  |  |  |

| 5     | ADC0RST  | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

|       |          |     | V-ADC Reset |  |  |  |

| 6     | ADC1RST  | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

| 7     | Reserved |     |             |  |  |  |

|       |          |     | UART Reset  |  |  |  |

| 8     | UARTRST  | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

|       |          |     | SHA Reset   |  |  |  |

| 9     | SHARST   | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

|       |          |     | IWDT Reset  |  |  |  |

| 10    | IWDTRST  | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

|       |          |     | WUPT Reset  |  |  |  |

| 11    | WUPTRST  | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

|       |          |     | EINT Reset  |  |  |  |

| 12    | EINTRST  | R/W | 0: Reset    |  |  |  |

|       |          |     | 1: Release  |  |  |  |

| 31:13 | Reserved |     |             |  |  |  |

## 3.4.8 System reset source status register (SYSCTRL\_RSTSR) Offset address: 0x1C

| Field | Name    | R/W | Description                     |

|-------|---------|-----|---------------------------------|

|       |         |     | WWDT Reset Source Flag          |

| 0     | WWDTRSR | R   | 0: No IWDT reset generated      |

|       |         |     | 1: IWDT reset generated         |

|       |         |     | IWDT Reset Source Flag          |

| 1     | IWDTRSR | R   | 0: No IWDT reset generated      |

|       |         |     | 1: IWDT reset generated         |

|       |         |     | SYSRSR Reset Source Flag        |

| 2     | SYSRSR  | R   | 0: No SYSRSTREQ reset generated |

|       |         |     | 1: SYSRSTREQ reset generated    |

| 3     | OPLRSR  | R   | Option-bytes Reset Source Flag  |

| Field | Name     | R/W | Description                               |

|-------|----------|-----|-------------------------------------------|

|       |          |     | 0: No option byte load reset generated    |

|       |          |     | 1: Option byte load reset generated       |

|       |          |     | Low Power Reset Source Flag               |

| 4     | LPRSR    | R   | 0: No Hibernate low-power reset generated |

|       |          |     | 1: Hibernate low-power reset generated    |

|       |          |     | POR Reset Source Flag                     |

| 5     | PORRSR   | R   | 0: No power-on/power-down reset occurs    |

|       |          |     | 1: Power-on/power-down reset occurs       |

| 31:6  | Reserved |     |                                           |

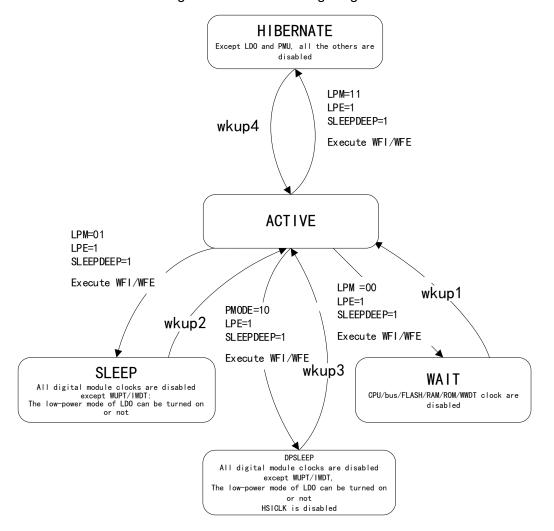

## 3.4.9 System low-power mode register (SYSCTRL\_LPMCR) Offset address: 0x20

| Field | Name     | R/W | Description          |

|-------|----------|-----|----------------------|

|       |          |     | Low Power Mode       |

|       |          |     | 00: WAIT status      |

| 1:0   | LPM      | R/W | 01: SLEEP status     |

|       |          |     | 10: DPSLEEP status   |

|       |          |     | 11: HIBERNATE status |

| 31:2  | Reserved |     |                      |

Reset value: 0x0000 0000

Note: This register will only reset during power-on reset, and the watchdog reset will be unaffected.

#### 3.4.10 System low-power configuration register (SYSCTRL\_LPCR)

#### Offset address: 0x24

| Field | Name      | R/W | Description                                                                                                                          |

|-------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

|       |           |     | LDO Low Power                                                                                                                        |

| 0     | LDO_LP    | R/W | 1: Enable                                                                                                                            |

|       |           |     | 0: Disable                                                                                                                           |

|       |           |     | HSI Low Power Select                                                                                                                 |

|       |           |     | When entering the DPSLEEP state, select the HSI status                                                                               |

| 1     | HSI_LPSEL | R/W | 1: Enter the ultra-low power state, with a frequency of<br>approximately 700kHz                                                      |

|       |           |     | 0: Sub-low power mode, with a frequency of approximately 1.4MHz                                                                      |

|       |           |     | Wait LDO                                                                                                                             |

|       |           | R/W | When LDO_LP is enabled and it exits from the SLEEP or<br>DPSLEEP state, it will wait for WAITLDO SYS_CK until<br>LDO becomes stable. |

| 7:2   | WAITLDO   |     | 0:1 clock cycle                                                                                                                      |

|       |           |     | 1: 2 clock cycles                                                                                                                    |

|       |           |     |                                                                                                                                      |

|       |           |     | N: N+1 clock cycles                                                                                                                  |

| 8     | LPE       | R/W | Low Power Enable                                                                                                                     |

Reset value: 0x0000 00FD

| Field | Name     | R/W | Description                                                                                                                                                                                                                                                            |

|-------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |          |     | Used for control of low-power state entry. 1 can only be<br>written to LPE when LPCR_KEY is equal to 0xA5A5.<br>When the system exits the low-power mode, the system<br>will automatically clear this bit to 0.<br>1: Enable entering the low-power mode<br>0: Disable |

| 15:9  | Reserved |     |                                                                                                                                                                                                                                                                        |

| 31:16 | LPCR_KEY | R/W | Low Power Key<br>When LPCR_KEY is equal to 0xA5A5, LPE can be written.                                                                                                                                                                                                 |

# 3.4.11 System communication start bit detection register (SYSCTRL\_STA)

Offset address: 0x28 Reset value: 0x0000 0008

| Field | Name      | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | STA_WUPEN | R/W | Start Wake-up Enable<br>This bit is determined based on the system configuration<br>COMM_MODE.<br>1: Enable<br>0: Disable<br>Note: Only when the PMU enters the HIBERNATE and<br>DPSLEEP status, will the I2C start bit or HSC-BREAK be<br>detected, and the hardware will pull down the SCL and<br>SDA pins; refer to STA_AUTO Settings for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1     | STA_AUTO  | R/W | Start Auto<br>When the system enters DPSLEEP status, if STA_WUPEN<br>is enabled, STA_AUTO will be configured to 1, and the<br>hardware will pull down the SCL and SDA pins (when<br>COMM is 1, pull down SCL; when COMM is 0, only pull<br>down SDA) until the software writes 1 to STA_WUPFCLR<br>and the I2C bus will be released. Otherwise, when STA_<br>AUTO is configured to 0, after PMU exits the DPSLEEP<br>status (i.e. the CPU is running instructions or the system is<br>exiting the reset), the system will release the bus.<br>When the system enters DPSLEEP status, if STA_WUPEN<br>is enabled, STA_AUTO will be configured to 0, and the<br>hardware will pull down the SCL and SDA pins (when<br>COMM is 1, pull down SCL; when COMM is 0, only pull<br>down SDA) until PMU exits Hibernate mode (i.e. CPU is<br>running instructions or the system is exiting reset), the<br>system will release the bus, and Hibernate mode<br>STA_AUTO will be set to 1 as an invalid value.<br>1: Manual mode<br>0: Automatic mode |

| 2     | STA_WUPIE | R/W | Start Wake-up Interrupt Enable<br>1: Enable<br>0: Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3     | COMM_MODE | R/W | Communication Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Field | Name     | R/W | Description                                                                                                        |

|-------|----------|-----|--------------------------------------------------------------------------------------------------------------------|

|       |          |     | 1: Select I2C mode                                                                                                 |

|       |          |     | 0: Select HSC mode                                                                                                 |

|       |          |     | Start Flag                                                                                                         |

| 4     | STA_FLAG | R/W | The value of 1 indicates the I2C start bit or HSC-BREAK is detected, and writing 1 to this bit can clear STA_FLAG. |

| 31:5  | Reserved |     |                                                                                                                    |

Note: This function will be used before entering DPSLEEP or HIBERNATE status. To prevent conflicts between STA detection and I2C/HSC module, STA detection is disabled in other scenarios.

#### 3.4.12 System wake-up flag register (SYSCTRL\_WUSR) Offset address: 0x2C

| Field                                   | Name      | R/W | Description                         |

|-----------------------------------------|-----------|-----|-------------------------------------|

|                                         |           |     | I2C Wake-Up Flag                    |

| 0                                       | I2C_WUF   | R   | 0: No I2C/HSC interrupt wake-up     |

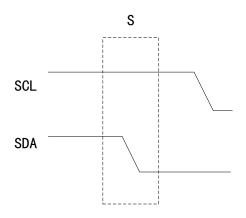

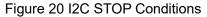

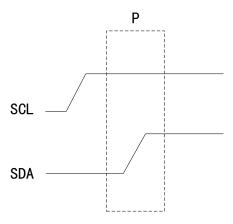

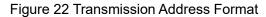

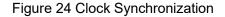

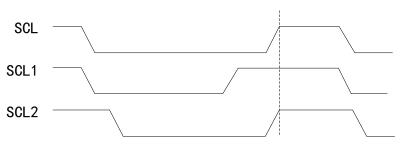

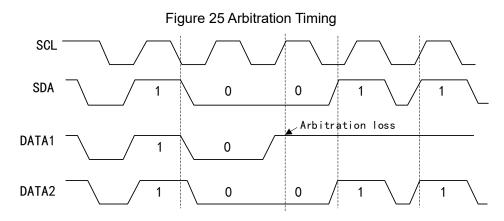

| , i i i i i i i i i i i i i i i i i i i |           |     | 1: I2C/HSC interrupt wake-up occurs |